祝 毅,鄭 斌,曾令昕,劉明凱,高 波,嚴 強

(中國星網網絡應用有限公司,重慶 401120)

0 引言

過去的一年,衛星互聯網的發展如火如荼,國外幾個星座項目取得了重大進展。Starlink 繼續擴大其星座的規模,在軌的衛星數量已經超過3 000 顆,除提供消費級服務外,其業務模式還擴展到海事和企業服務。此外,Oneweb 星座衛星的數量也達到了462 顆,其在幾個關鍵市場都取得了進展。歐盟于2022 年宣布了一項60 億歐元的低軌通信星座計劃,而中國更是通過了一系列法律、法規支持民營企業建造低軌通信衛星。衛星、電信服務和智能手機行業都朝著正確的方向邁出了一大步。更具有影響力的是,蘋果公司在2022 年9 月的iPhone 14 發布會上宣布,該手機可與Globalstar 衛星連接,初期可用于緊急求救消息的發送。SpaceX 和T-mobile也宣布了衛星直接與手持通信設備的合作。華為宣布其Mate50 智能手機將能夠使用中國北斗衛星導航發送短報文,后續將進一步支持短語音通話。這些領域中不斷出現的技術突破在衛星移動通信業界掀起了新的熱潮[1]。

衛星移動通信領域的專業技術包含廣泛,涉及衛星、運營以及終端等各個環節。從通信、網絡到終端設備都有巨大的研究空間。其中,終端基帶處理作為衛星通信終端的核心能力,更是承載著衛星移動通信端測發展的重任,是實現衛星移動通信商業化發展必須突破的重要技術方向。當前國外的衛星終端基帶公開資料較少,但從零星的報道和其終端的商業化程度來看,其技術成熟度已達到較高水平。伴隨著天通衛星通信系統的發展,國內的衛星終端基帶也積累了一定的技術成果[2]。但是隨著衛星體制的發展演進變化,終端面臨著多體制、多載波的更高更強的處理要求,因此對終端基帶的設計也帶來了挑戰。對于基帶處理而言,要解決多種體制信號的兼容性接收,就必須要具備靈活可配置的數字前端。數字前端作為模擬域與基帶處理之間的橋梁,是軟件無線電體系架構下基帶處理不可或缺的一部分。數字前端的主要任務是負責數模轉換后的采樣率變換、數字上下變頻、數字濾波等功能。同時還要考慮并行載波的聚合分離,就必須要具備并行處理能力。除此之外,還要兼顧基帶處理資源對于功耗和面積的影響因素,這就對數字前端整體的設計有了更多的細節要求,因此對前端鏈路中的每一個模塊都需要精心考慮。

1 基帶處理介紹

基帶處理是整個移動衛星通信上最核心的部分,可以用來發射合成以后的基帶信號,或者對接收來自空口的基帶信號進行解調譯碼。如圖1 所示,數字接收機基帶處理一般包含多個功能組成,如數字前端、時頻同步、解交織、解擾/信道編譯碼等[3]。數字前端在模數轉換后的第一步是完成信號的子載波分離,是保證信號質量的關鍵環節,一般以硬件實現,軟件實現往往無法滿足實時性的要求。時頻同步需要用到信號估計等實現時間和頻率的糾正,但是其算法復雜度高且變化較多,因此通常軟硬件結合。信道編譯碼一般為通信中計算要求較高的部分,如Turbo 譯碼、低密度奇偶校驗碼(Low Density Parity Check Code,LDPC)譯碼,所以需要以硬件的方式來提高處理效率[4]。其他的交織和擾碼等計算均有標準的格式,復雜度也不高,所以在實際工程中也比較容易實現。

圖1 基帶處理過程

針對當前衛星移動通信系統不同體制的兼容性問題,同時為了拓展收發設備的通信場景和通信能力,在基帶處理設計時做出了一定的改進,以便未來適應多模多制式的應用[5]。后文將重點闡述基帶處理中數字前端(Digital Front-End,DFE)的詳細設計和仿真研究內容。

2 數字前端設計

2.1 DFE 收發鏈路組成

DFE 作為衛星終端基帶處理的重要組成之一,可以提高數據的處理效率,降低信號處理的時延。DFE 主要實現濾波、混頻、抽取等功能,從而把數據的采樣率降低到較低水平,以便處理核心進行軟件處理。因此,在設計時,要綜合考慮入口數據速率、系統帶寬、信號帶寬和實際應用等因素。

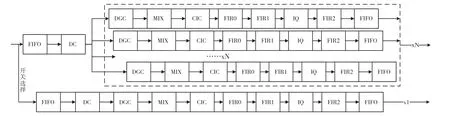

DFE 包含接收和發送兩條主要的信號處理鏈路。其中接收鏈路對入口的采樣數據經過直流矯正、數字下變頻、積分梳狀(Cascaded Integrator-Comb,CIC)抽取濾波、后級有限沖激響應(Finite Impulse Response,FIR)數字濾波、同相正交(In-phase and Quadrature-phase,IQ)矯正、匹配濾波等處理變為較低采樣率的數據。接收鏈路采用“N+1”的結構,包括一路單載波和擴頻復合處理分支,另外N路分支完成多路載波分離的功能。發送鏈路有成型濾波、二級濾波、CIC 內插、上混頻、IQ 校正等功能,發送鏈路需要完成多路載波聚合處理,還需要具備單載波處理能力[6]。DFE 中的各級模塊都具有可變配置參數,通過總線完成對應的參數配置,實現對應物理層波形的收發功能。

如圖2 所示為基帶處理的多通道DFE 接收鏈路設計,圖中包含多通道的部分和單通道的部分,這兩種部分可以切換,通過寄存器配置參數選通其中一路。多通道部分可以完成多個子載波等不同組合情況下的載波分離處理,其中各個通道的參數可以單獨配置,也可以關斷,通道之間組合方式靈活多變,處理結果和過程保持高度一致性。單通道部分僅含處理單個載波的各個資源子模塊,針對低速單載波和高速的擴頻模式進行了兼容性考慮,擴大了參數配置和處理能力范圍。所有接收鏈路中的子模塊均具備旁路功能,即設置相應的旁路寄存器就可以使信號數據不經過當前子模塊的處理,直通到下一級子模塊。

圖2 DFE 接收鏈路設計

如圖3 所示為基帶處理的多通道DFE 發送鏈路設計框圖。與接收鏈路類似,發送鏈路也包含多通道部分和單通道部分,不同在于信號處理流向相反。接收是處理來自射頻接口的數據,并將輸出通過直接存儲訪問(Direct Memory Access,DMA)搬移到內存。發送是通過DMA 反向搬移數據到模塊處理,最后從射頻接口輸出。發送鏈路的多通道輸出,最后通過合并模塊將數據合并以后送往射頻接口,各個通道也是獨立參數配置和獨立工作。單載波通道更加簡化,省去了一級濾波,優化了鏈路資源消耗,參數也可以靈活配置。

圖3 DFE 發送鏈路設計

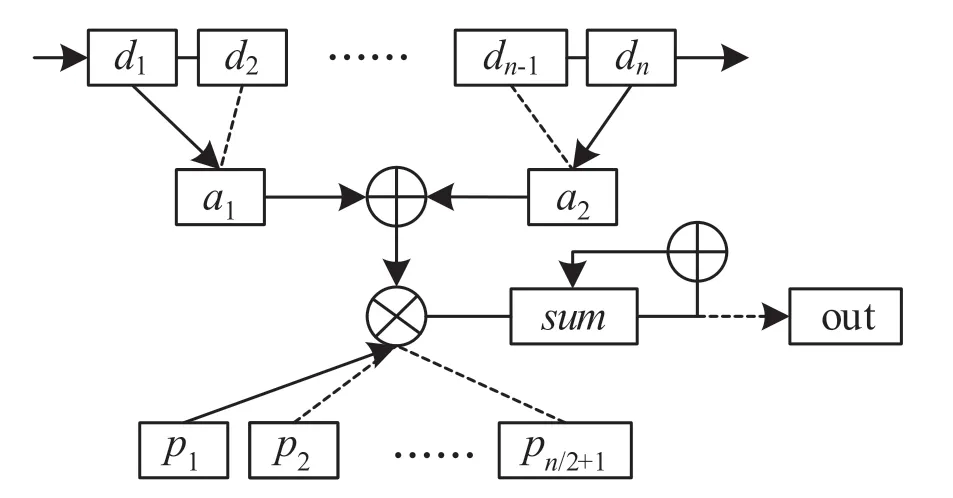

2.2 FIR 濾波器

數字FIR 濾波器被經常用于前端處理,用于改善信號的質量。對應信號速率的改變,接收需要進行抽取濾波,發送需要進行內插濾波,抽取和內插因子的設置范圍要足夠覆蓋寬窄帶波形。此外,通常在一個鏈路設計中需要放入多級濾波結構,濾波器的階數可以根據物理層波形設計,但需要盡可能壓低濾波器階數,從而降低資源消耗。傳統的FIR直接型濾波結構在計算時,其參與的乘法器和加法器個數與濾波器階數有關,階數越高消耗的乘法和加法越多。在實際工程中,為了降低資源消耗,可以采取一些設計技巧,利用高速率時鐘,以時間換取空間的做法,結合選通器,利用單個乘法和加法就可以實現濾波器的完整運算。如圖4 所示,d為串行數據流,p為濾波器系數,sum為求和結果。分別選擇濾波系數和串行數據,依次進行相加相乘,乘法結果再進行累加求和,最終輸出一個濾波結果。如此結構的濾波器消耗的資源可以降低很多。

圖4 FIR 濾波簡化計算模型

2.3 數字混頻器

數字混頻器一般用于頻譜搬移,在信號接收過程中,將低中頻的數字信號變到零頻,在發送的過程中,把零頻信號搬到目標頻點上。一般傳統的做法是將信號與本地載波相乘,這樣就需要產生本地載波,不僅需要消耗乘法器資源,還需要占用較大空間的存儲資源。這里借助坐標數字旋轉計算(Coordinate Rotation Digital Computer,CORDIC)的思想,對要混頻的每個復信號采樣點進行旋轉,旋轉角度按照頻率控制字累加。頻率控制字的計算方式如下[7]:

式中:f0為混頻目標頻率;fs為信號采樣率;N為頻率分辨位寬;Δ為頻率控制字。

而在使用CORDIC 算法計算時,相位控制字隨著采樣數據逐點計算不斷累加,在累加過程中,由于定點化位寬限制,累加值在溢出后自動補償到新的相位控制值,然后每一個復信號點就會以對應的θ(n)進行旋轉,其計算公式如下:

式中:θ(n)為第n個點需要旋轉相位;θ0為初始相位一般為0;Mod 為取模操作。

計算出相位以后,就可以使用CORDIC 迭代算法將矢量旋轉到某個角度目標[8]。那么旋轉矩陣可以表示為:

式中:Rn(θ)為旋轉矩陣;θn為旋轉相位。

為了便于硬件處理,通過以下三角恒等式等效轉換。

通過限制tan(θn)=2-n,當其為2 的冪次方后,在硬件上就是簡單的移位操作。通過這種限制,在硬件上基本就不需要任何資源的結構,這對于工程實現來說是一個巨大的優點。同時由于又受限于旋轉角度,為了實現任意角度,就不得不實現多次旋轉迭代,最終趨近于目標值。旋轉過程中還要注意區分是正向還是逆向的旋轉。這樣的操作概括為:

式中:xi-1,yi-1為前一次旋轉后的復信號實部和虛部;Ki為增益因子;σi為正負1 代表旋轉方向。

在模塊處理初始時需要對增益因子進行補償,迭代多次增益趨近于一個穩定值。那么補償值為該近似趨近值[9]。求極限如下式:

一般工程上,要達到較好的精度要求,通常要求迭代14 次以上。混頻器的輸入信號幅度也需要控制在較好的線性范圍內,信號太小則量化誤差 較大。

2.4 積分梳狀線濾波器

CIC 濾波器已經應用較多,一般在信號帶寬比較寬、采樣抽取或內插倍數比較高的時候,FIR 濾波器的使用性價比就不是特別高了,所以選用CIC來實現高倍數的采樣率變換可以有效降低資源,減小電路面積。

對于CIC 濾波器的設計,主要關注抽取和內插因子、濾波級聯數、延時因子這幾個指標。由積分器和差分器級聯的傳遞函數[10]表示為:

式中:N為濾波器級聯階數;D為抽取因子;M為延時因子,一般為1 或2,通常選1。

隨著CIC 級數的增加,其阻帶衰減也會增加,帶內衰減也伴隨著增加。因此,在多級級聯時,為了獲得良好的通帶平坦特性,一般設計CIC 濾波器的級數不超過5 級。另外,考慮到實際使用上的靈活性,CIC 濾波器的級數為4 級或5 級可選擇。抽取和內插因子也設計為1~256 可配置。

在CIC 的計算過程中,會產生位寬擴展,使輸入信號有增益。位寬擴展計算如下:

式中:Bin為輸入數據位寬;Bout為輸出數據位寬;為向上取整。

CIC 的中間過程為了適應全動態范圍,需要保持最大擴展位寬精度計算,在輸出結果時根據抽取或內插因子截位。例如位寬[B:0]截取n位,那么輸出[B:n]+[n-1]作為最終輸出結果,這樣的截位方式與四舍五入nearest()函數等效。

2.5 增益控制模塊

數字增益控制(Digital Gain Control,DGC)是保證數字前端信號收發幅度可控的關鍵模塊。使得信號能夠按照預定幅度要求發送至天線,接收信號在基帶達到預定范圍便于后級運算處理。這里采用開環方式,由總線配置寄存器增益值和截位參數,通過乘法和移位計算以達到目標增益精度的要求。具體計算公式如下:

式中:x(n)為輸入信號;y(n)為輸出信號;G為增益 值;A為寄存器配置增益參數;i為移位位數。

在實際計算過程中,參數配置的增益值只會近似目標增益值,在工程上達到可接受的誤差范圍 即可。

2.6 IQ 矯正模塊

在實際應用過程中,由于受器件工藝的限制,在同相支路和正交支路上的濾波器、混頻器等模擬器件無法保證一致性。進而導致I 路和Q 路信號相應存在一定的差異,主要表現為鏡像頻譜分量、星座點失衡、信號嚴重失真,使整個通信系統的動態范圍和靈敏度下降。

為了解決上述問題,專門設計了IQ 矯正模塊,通過配置矯正因子來糾正IQ 不平衡的問題。首先提前估計出幅度和相位不平衡參數[11]:

式中:yI(n),yQ(n)為同相和正交分路的采樣信號;α為幅度矯正因子;φ為相位矯正因子。

上述矯正因子在提前估算出以后,通過寄存器的方式寫入配置參數。為了減少在硬件上實現三角函數的運算,可以對矯正因子計算以后整體配置乘法項。

2.7 直流矯正模塊

由于器件工藝、本振泄露、天線、溫度等多種因素都會導致零中頻接收機產生直流偏置,所以在接收處理支路上需要進行直流矯正。工程實現時,利用信號的統計特性對其直流偏置值進行估計,I、Q 兩路的直流偏置估計值[12]為:

在得到直流估計值以后,通過矯正公式扣減直流分量。在實際工程中,可以提前根據電路啟動估計流程,采樣底噪作為樣本,然后把提前估計值存儲在寄存器里,作為后續空口收發的矯正值。也可以用軟件控制實時矯正。

式中:IDC(n),QDC(n)為矯正以后的同相和正交支路采樣信號。

3 鏈路參數仿真

基于前述的DFE 收發鏈路設計,配置不同載波場景進行鏈路參數仿真,包含收發通道的幅頻響應以及收發信號的誤差向量幅度(Error Vector Magnitude,EVM)評估。

3.1 發送鏈路仿真

配置場景1:單載波發射通道,輸入符號速率Rd1,輸出信號采樣率fs1,滿足fs1=4Rd1關系。

配置場景2:多載波發射通道,輸入符號速率Rd2,輸出信號采樣率fs2,滿足fs2=256Rd2關系。

配置場景3:多載波發射通道,輸入符號速率Rd3,輸出信號采樣率fs3,滿足fs3=1 280Rd3關系。

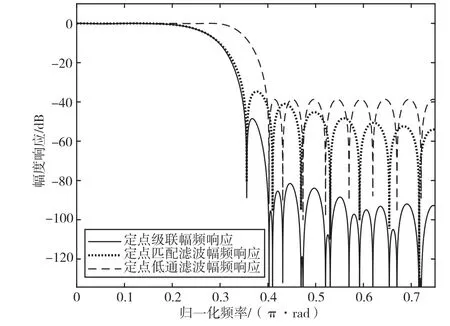

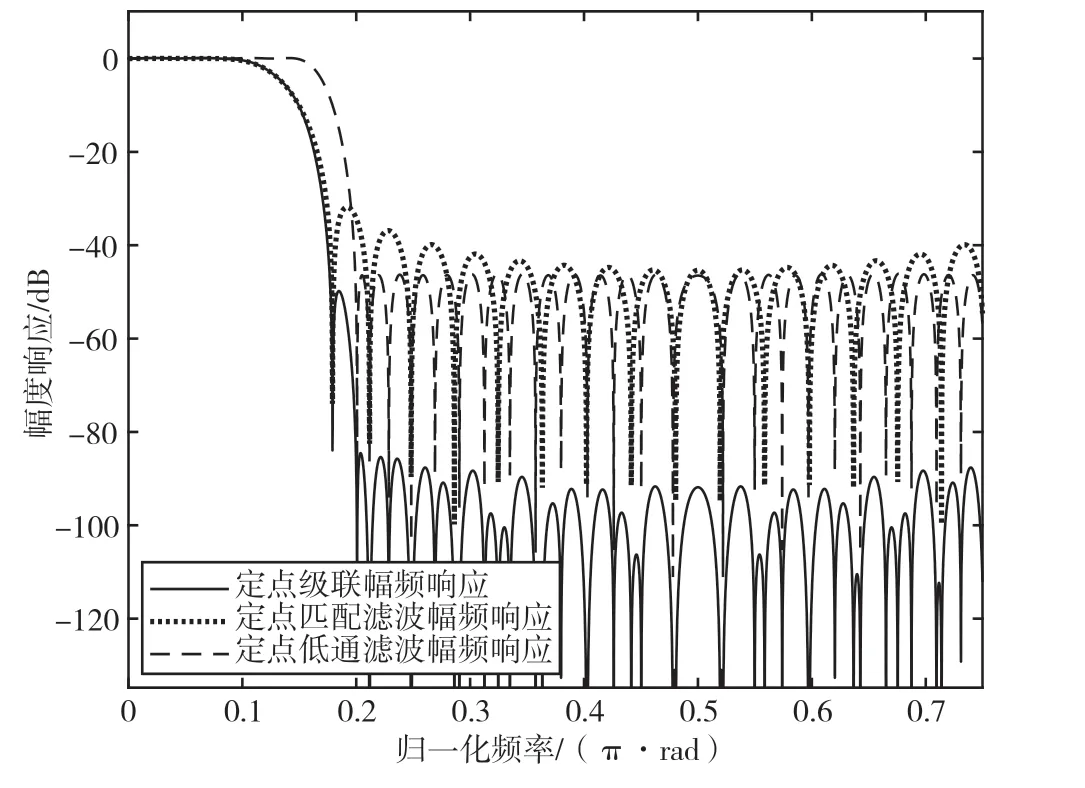

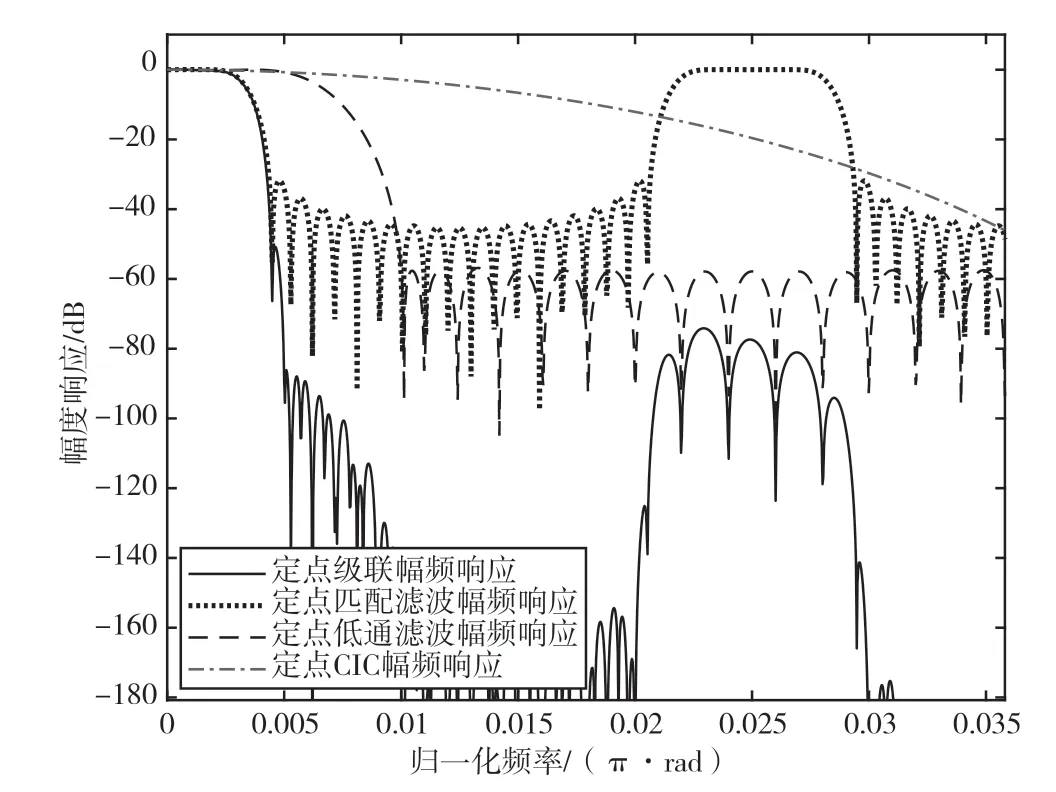

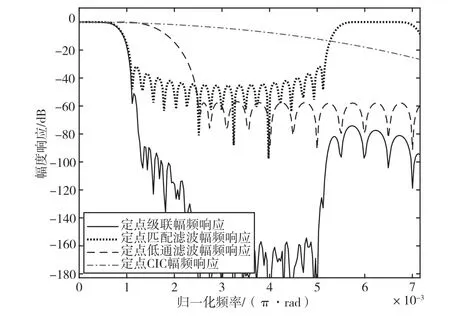

以上仿真場景分別如圖5、圖6、圖7 所示,表示不同發送場景下的通道幅頻響應,可以發現通道的通帶和阻帶指標都比較優,定點算法的性能與浮點接近,完全可以硬件實現。

圖5 發送場景1 的定點幅頻響應

圖6 發送場景2 的定點幅頻響應

圖7 發送場景3 的定點幅頻響應

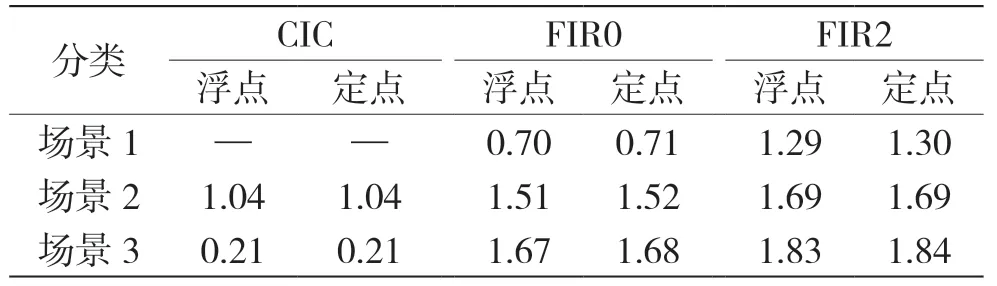

再對比發送通道不同場景下的EVM,信號調制方式采用正交相移鍵控(Quadrature Phase Shift Keying,QPSK),鏈路中節點仿真結果如表1 所示。

表1 發送鏈路EVM 仿真結果/%

從表1 可以看出,定點算法鏈路的EVM 性能接近浮點,誤差在0.01 左右。

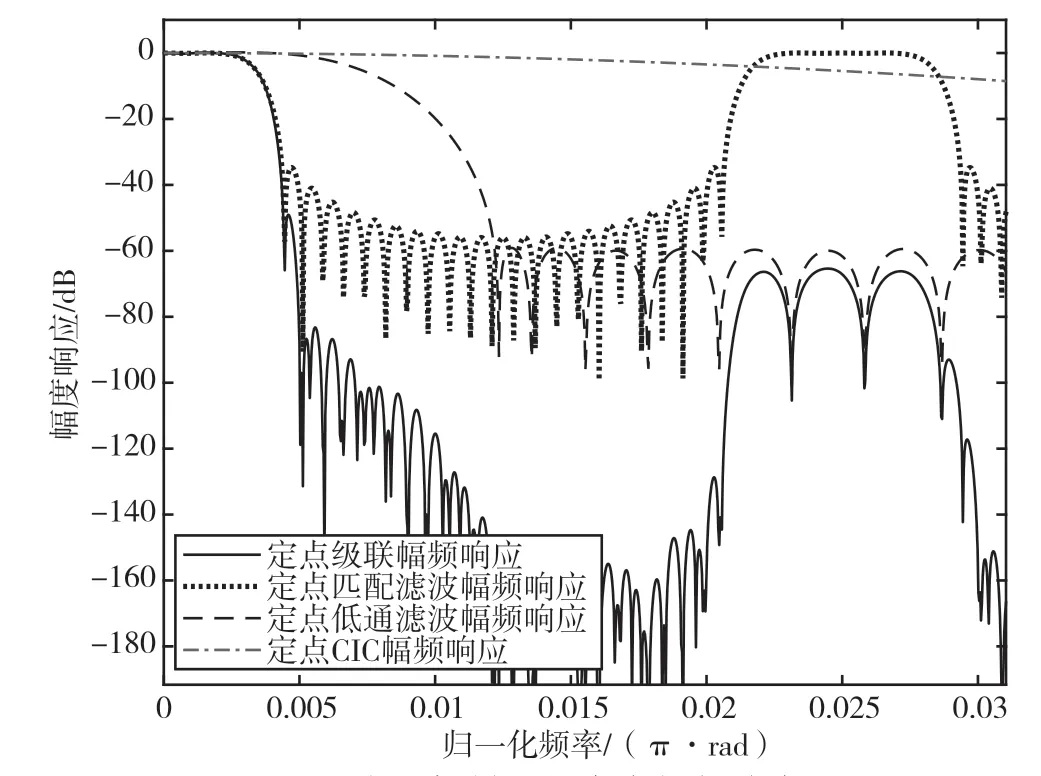

3.2 接收鏈路仿真

同樣針對接收通道也做了同類場景的仿真。如圖8、圖9、圖10 所示,分別為以下3 種場景的幅頻響應。其性能與浮點一致,響應特性曲線的性能 較好。

圖8 接收場景1 的定點幅頻響應

圖9 接收場景2 的定點幅頻響應

圖10 接收場景3 的定點幅頻響應

配置場景1:單載波接收通道,輸出符號速率Rd1,輸入信號采樣率fs1,滿足fs1=4Rd1關系。

配置場景2:多載波接收通道,輸出符號速率Rd2,輸入信號采樣率fs2,滿足fs2=256Rd2關系。

配置場景3:多載波接收通道,輸出符號速率Rd3,輸入信號采樣率fs3,滿足fs3=1 280Rd3關系。

接收通道不同場景下的EVM,信號調制方式采用正交相移鍵控QPSK,仿真結果如表2 所示。

表2 接收鏈路EVM 仿真結果/%

4 結語

根據衛星移動通信發展對基帶處理多體制多載波的傳輸要求,設計了一種“N+1”的數字前端融合收發鏈路。分析和闡述了鏈路中各個主要模塊的數學原理和優化設計,極大地降低了其在數字基帶設計中的資源消耗,在工程設計中結合電源控制技術進一步降低模塊功耗。該數字前端鏈路結構具備靈活多變的可配置特性,通過仿真分析了收發鏈路在不同場景下的幅頻響應和EVM 等參數特性。可以看出,收發鏈路的幅頻響應均滿足各個場景的使用,EVM 惡化也較低,定點算法與浮點算法相匹配,完全滿足工程設計要求。