0 引言

CAN(Controller Area Network)是由ISO定義的一種串行通信總線,它是一種能有效地支持高安全等級的分布實時控制的新一代網絡通信協議,屬于現場總線范疇。CAN最早被設計作為汽車環境中微控制器的通訊,在車載各電子控制裝置與ECU之間交換信息,形成汽車電子控制網絡,目前應用領域已經相當廣泛。

近年來,支持CAN協議的芯片不斷推出,給CAN總線用戶帶來了極大的方便。隨著我國對現場總線技術需求的增加,CAN總線已經會成為我國最常用的現場總線之一。

基于CAN總線的ECU電子控制單元的開發,也是現在最熱門的研究。現在對CAN總線芯片的研究已經不再局限于單一芯片的研究,而是把所有的功能芯片都集中在一塊芯片上實現一個完整的ECU的功能。

本項目目的是利用FPGA實現一款支持CAN2.0協議的總線控制器,完成一個通用的能夠滿足CAN2.0協議的CAN總線控制器軟IP核,這樣可以在以后的應用中方便的集成到其他系統中去。本文使用VerilogHDL語言,設計了一款支持CAN2.0協議的CAN總線控制器,并利用FPGA芯片在CAN總線網絡中對其進行了測試,實現了設計目的。創新點為CAN_Registers設計中寄存器模塊、位流處理器的收發部分功能、測試程序、基于該FPGA的CAN總線控制器的節點電路等。

1 CAN總線控制器設計

1.1 CAN控制器設計流程

1.1.1 功能設計

首先對CAN2.0協議進行了深入的分析,掌握了CAN總線協議的各部分內容;而后參照和分析了幾種典型的CAN總線控制器的功能;最后選擇PHILPS公司生產的CAN總線控制器SJA1000進行進一步的分析,掌握了它的各部分模塊的功能。在這些基礎上根據需要規劃了所設計的CAN總線控制器的功能。

1.1.2 設計描述和功能驗證

功能設計完成后,依據功能并參照CAN總線2.0協議,將控制器劃分為若干功能模塊,明確了各個功能模塊的作用。確定模塊及其功能之后,用Verilog HDL語言實現了各模塊的設計。接著,利用Modelsim對整個設計進行了功能驗證。

1.1.3 邏輯綜合

功能仿真通過以后,利用QuartusⅡ對所設計的CAN總線控制器進行邏輯綜合,并把其配置到FPGA中。

1.1.4 硬件驗證

配置到FPGA中以后,用所設計的基于FPGA的CAN總線控制器作為一個節點,與采用SJA1000作為控制器的節點電路進行了通信測試,驗證了所設計的CAN總線控制器的功能。

1.2 CAN總線控制器的整體設計

1.2.1 控制器SJA1000的功能結構

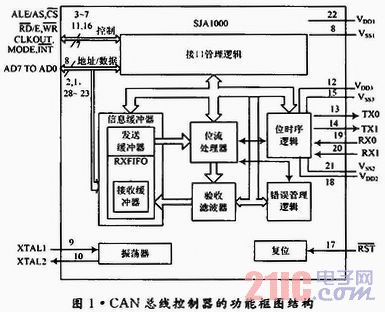

SJA1000是PHILIPS公司于1997年推出的一種獨立CAN總線控制器,用于汽車和一般環境中的控制器局域網絡。SJA1000主要由以下幾個部分構成:接口管理邏輯、發送緩沖器、接收緩沖器、接收濾波器、位數據流處理器、位時序邏輯、錯誤管理邏。SJA1000是雙列直插式集成電路,功能框圖如圖1所示。

1.2.2 本文中控制器的功能結構

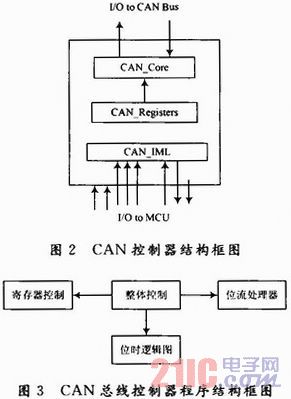

本文設計的CAN控制器參照SJA1000控制器的結構,功能基本框架包含如圖2所示的3個功能模塊。

CAN_IML是CAN總線控制器接口邏輯,主要功能是解釋來自微處理器的命令,控制CAN寄存器的尋址,向微處理器提供中斷信息和狀態信息。

CAN_Core為CAN協議控制器的核心部分,完成CAN協議中的數據鏈路層的全部功能以及物理層的部分功能,包括LLC子層的接收濾波、超載通知和恢復管理、MAC子層的數據封裝/拆裝、幀編碼、媒體訪問管理、錯誤檢測、錯誤標定、應答和串行化/解串行化、以及物理層的位編碼/解碼、位定時和同步。CAN_Registers為一寄存器組,外部微處理器可以通過地址直接訪問這些寄存器。根據功能框圖,設計了CAN總線控制器的程序結構,如圖3所示。

1.3 CAN總線各個功能模塊的設計

1.3.1 CAN_IML設計

參照SJA1000,設計FPGA CAN總線控制器的接口,如圖4所示。

圖中Port_0_io_7到Port_0_io_0為地址/數據復合總線。Cs_can_i為片選輸入信號。當Cs_can_i為0時允許訪問CAN總線控制器。Ale_i為1時,允許對寄存器進行賦值。Rd_i和Wr_i為微處理器的讀使能信號和寫使能信號。Irq_on為中斷輸出信號,用于中斷微處理器。Rst_i為復位輸入,用于復位CAN接口。Clkout_o為FPGA CAN控制器提供給微處理器的時鐘輸出信號,時鐘分頻寄存器可禁止該引腳輸出。Bus_off_on控制總線關閉和總線開放接口,Tx_o和Rx_i與收發器相連,向總線發送和接收數據。

1.3.2 CAN_Registers設計

設計的CAN總線控制器的寄存器模塊包括以下寄存器:模式寄存器、命令寄存器、狀態寄存器、中斷寄存器、中斷使能寄存器、總線定時寄存器0~1、仲裁丟失捕獲寄存器、錯誤代碼捕獲寄存器、錯誤報警限制寄存器、接收錯誤計數器、發送錯誤計數器、驗收代碼寄存器0~3、驗收屏蔽寄存器0~3、接收信息計數器和接收/發送緩沖器。

1.3.3 CAN_Core設計

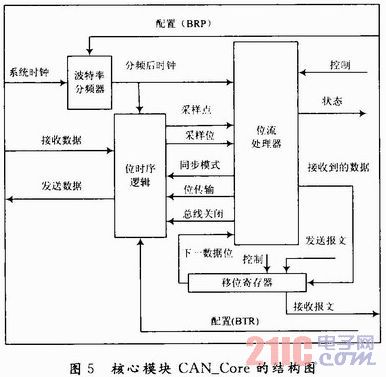

CAN_Core為整個CAN控制器的核心,負責處理CAN的協議。核心模塊由4個部分組成,結構如圖5所示。

下面簡單介紹CAN_Core模塊中的位流處理器、位時序邏輯。

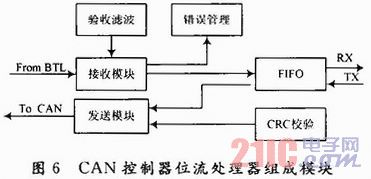

位流處理器是CAN總線控制器中控制數據流的發生器。它還執行總線上的錯誤檢測、仲裁、填充和錯誤處理等功能。主要有接收模塊、發送模塊、錯誤管理模塊、CRC校驗、驗收濾波、FIFO等6個模塊組成,如圖6所示。其中CRC校驗、FIFO、驗收濾波在所執行的項目中已經有他人設計完成。

位時序邏輯的設計包括位定時設計、采樣點設計、位同步設計3部分。下面以定位時為例介紹其設計。

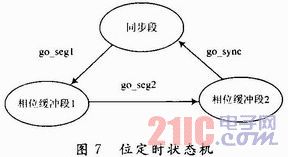

位定時設計 在位定時設計中采用了一個有3個狀態的狀態機。3個狀態分別對應的是同步段和相位緩沖段1以及相位緩沖段2。傳播段占用的時間短,在控制上沒有特別的意義,僅作為物理層的傳播延時,所以沒有設計進狀態機,位定時部分的狀態機設計如圖7所示。

接著使用ModelSim軟件對所設計的各個模塊和整個CAN總線控制器進行了功能仿真,仿真結果表明達到了設計目標。

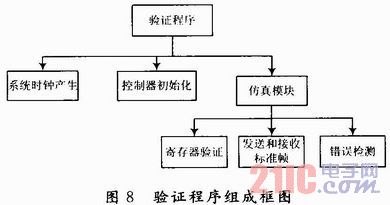

2 測試驗證

本文最后設計了CAN總線控制器的測試程序,其目的是模擬一塊微處理器對CAN總線控制器進行讀寫操作,從而實現對CAN總線控制器的寄存器訪問,完成總線收發功能。在該測試程序編寫中,各個功能基本上以任務的形式實現,進行不同的仿真時只需調用相關的任務模塊。圖8為驗證程序的組成框圖。

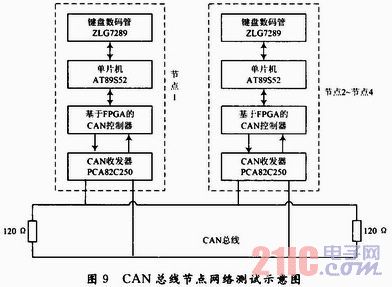

仿真驗證完成以后將其HDL CAN總線程序下載到FPGA中進行測試,目標芯片采用Cyclone系列的EP1C6Q240C8,為了驗證所設計的FPGA CAN總線控制器,還設計了一款基于該FPGA的CAN總線控制器的節點電路,然后利用所設計的節點電路與其他3個利用SJA1000作為控制器的CAN總線節點進行了通信測試。所有的節點使用AT89S52單片機作為節點微處理器,PCA82C250作為收發器,測試結果表明下載到FPGA中的控制器程序工作正常,實現了預計的CAN總線通訊功能。測試網絡示意圖如圖9所示。

測試時,按動節點1上的開關并將該狀態發送到節點2,在節點2上能顯示對應的狀態,反之也可。同時也可在節點2通過鍵盤輸入某一代碼,而在節點1上的數碼管上顯示相應的結果。該實驗結果表明下載到FPGA中的控制器程序工作正常。

3 結語

本項目利用Verilog HDL語言設計了一款CAN總線控制器芯片,并使用ModelSire軟件對所設計的CAN總線控制器進行了功能仿真;之后為了驗證設計,還編制一個驗證程序,并將驗證之后的設計配置到了FPGA中;最后用所設計的基于FPGA的CAN總線控制器制作了CAN節點,并與其他采用SJA1000為控制器的CAN節點進行了通訊測試,實現了CAN總線良好的工作,驗證了設計的正確性。